Review: Novel Assemble Approaches for 3D Devices Stacks

1. 題目與摘要

Title: Novel Assembly Approaches For 3D Device Stacks

Author: Laura Peters, Semiconductor Engineering (2025-06-30)

Executive Summary:

這篇文章聚焦於最新在 ECTC 2025 大會中展示的 3D 晶片封裝創新技術,強調隨著 AI 訓練與推理需求大幅攀升,3D 封裝成為解決熱管理與頻寬瓶頸的關鍵。文中介紹了多家領先企業如 Intel、TSMC、Georgia Tech 等的技術突破,包括 1µm hybrid bonding、晶片內冷卻、光電共封裝(CPO)等。整體趨勢顯示,3D 堆疊正從概念驗證進入實質量產準備階段,並將重新定義 HPC 與 AI 系統的散熱與訊號架構。

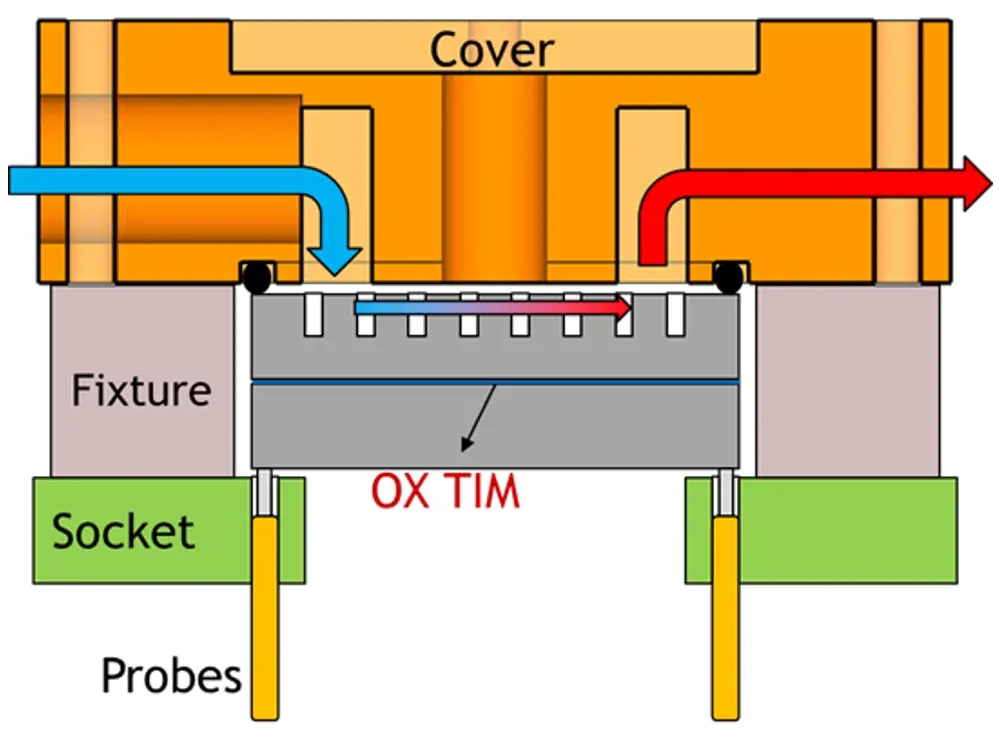

[[ Fig 1: TSMC CoWoS 液冷封裝模組原型圖,展示導入晶片底部冷卻液通道結構 ,TSMC 液冷封裝橫截面圖示,顯示冷卻液由蓋板進入後直接通過晶片底面區域進行散熱,並透過 OX TIM 加強熱導效率(圖片來源:TSMC Interconnect Research) ]]

🔍 圖片說明:

這是一個 液冷散熱封裝模組的橫截面示意圖,圖中要素包括:

元件 | 說明 |

|---|---|

Cover | 液冷蓋板,內含冷卻液流道 |

藍色箭頭 | 冷卻液進入路徑(冷流) |

紅色箭頭 | 冷卻液排出路徑(熱流) |

中間白色結構 | 晶片堆疊區域,可能含有 SoC / HBM |

OX TIM | 氧化物熱介面材料(thermal interface material),幫助導熱 |

Fixture / Socket / Probes | 封裝與測試用夾具與連接器 |

2. 背景與重要性說明

- AI、HPC(高效能運算)正快速推升晶片堆疊密度與功率密度。

- 2D 封裝與傳統空冷無法滿足高熱流密度晶片的散熱需求。

- 晶片堆疊與 chiplet 架構崛起,使熱、頻寬、訊號延遲成為核心瓶頸。

- 因此,需要創新封裝與散熱設計,從材料、結構、冷卻方式全面革新。

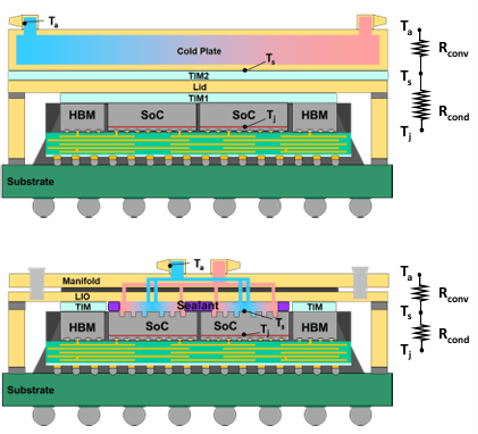

[[ Fig 2: Imec 與 TSMC 於 ECTC 2025 比較傳統 CoWoS 封裝(上)與直接液冷設計(下)之熱流與冷卻架構,指出後者可顯著提升散熱效率(出自 IEEE ECTC 2025, 引用自 Semiconductor Engineering) ]] (CoWoS with direct liquid cooling using 10 L/min water (below) dissipates more heat than CoWoS with TIMs, lid, and cold plate configuration. Source: IEEE ECTC [1])

這張圖展示的是 兩種不同的晶片散熱架構設計比較,常見於高效能 3D IC(如 SoC + HBM 組合)封裝中。圖中搭配了熱阻模型(thermal resistance network)來解釋熱流通路。

🧊 上圖:傳統冷卻方式(Cold Plate + Lid)

結構說明:

- Cold Plate:傳統水冷散熱片,與外部冷卻系統連接

- Lid(蓋板):金屬蓋,中間靠 TIM(熱介面材料)與晶片傳熱

- TIM1 / TIM2:熱介面材料,分別填補 SoC–Lid 與 Lid–Cold Plate 間隙

- SoC / HBM:處理器與高頻寬記憶體模組

- Substrate:基板

熱路模型:

- 熱從 Tj(junction)→ Ts(表面)→ Ta(冷卻液) 傳遞

- 所經熱阻:R_cond(導熱)+ R_conv(對流)

- 中間經過多層介質(晶片→TIM1→Lid→TIM2→Cold Plate)

💧 下圖:嵌入式液冷(Integrated Liquid Cooling)

結構說明:

- Manifold + Sealant:直接在 SoC 上方整合冷卻液流道,靠封裝密封劑隔絕

- 冷卻液流入/流出管道:直接與 SoC 表面接觸進行冷卻

- TIM 較少或無需蓋板:降低熱阻層數

- 熱從晶片內部更快散出

熱路模型:

- 熱從 Tj → Ts → Ta 傳遞,但此設計中 Ts 幾乎 = Tj

- 對流熱阻 R_conv 更貼近熱源,導熱路徑更短、更快

🔍 重點比較:

項目 | 傳統冷卻架構 | 嵌入式液冷架構 |

|---|---|---|

散熱距離 | 長,多層材料 | 短,直接與 SoC 表面接觸 |

熱阻 | 高(TIM1+Lid+TIM2) | 低(直接對流) |

液冷導入難度 | 外部冷卻模組即可 | 封裝需支援冷卻通道與密封結構 |

適用於 | 中低功耗封裝 | 高功率密度 3D 堆疊晶片 |

技術挑戰 | 成熟,但熱阻仍偏高 | 精密封裝整合與材料可靠性要求高 |

📌 這張圖的核心目的:

說明隨著 SoC + HBM 3D 堆疊功率密度提升,傳統冷卻方式已逐漸無法滿足熱通量需求,嵌入式液冷成為下一代趨勢。

3. 主要創新與技術亮點

公司/機構 | 技術亮點 | 重點內容 |

|---|---|---|

Intel | 1µm hybrid bonding | 低 pitch Cu-Cu bonding,提升訊號密度與熱傳導 |

TSMC | CoWoS with direct liquid cooling | 晶片底部導入液冷通道,可支援 4 SoC + 6 HBM 堆疊結構 |

Georgia Tech | chiplet-as-coolant | 將晶片視為冷卻通道本體,透過 TSV/矽中微通道實現液冷 |

Brewer Science / ITRI | 多層聚合物 RDL with hybrid bonding | 展示 10 層結構,整合銅與聚合物導體,實現超密度重分佈層(RDL) |

Corning / Fraunhofer | 光波導玻璃基板 | 作為 CPO 基板,兼容光電整合並維持熱穩定性 |

Samsung | 散熱強化封裝 | 導入高熱導銅底板技術,應用於 DRAM 與行動處理器 |

Imec | 熱模擬與功率分佈分析 | 進行多晶粒封裝熱管理建模與實驗,以評估高熱密度區域與冷卻效益 |

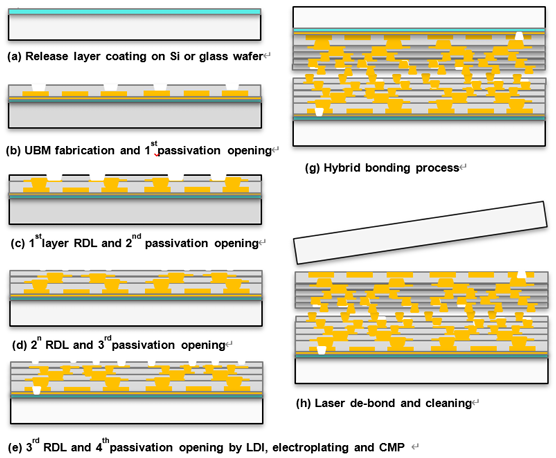

[[ Fig 3: Intel hybrid bonding 橫截面圖示,呈現 1μm Cu-Cu 鍍層與對位結構 , Intel hybrid bonding 封裝製程流程圖,展示多層 RDL 製作後,進行 Cu-Cu 混合鍵結並對位整合(圖片來源:Intel 於 IEEE ECTC 發表之封裝技術論文)

📌 圖片說明與流程:

這是 Intel 在其先進封裝流程中所採用的 Hybrid Bonding 製程的流程橫截面圖解,具體說明如下:

圖塊步驟 | 說明 |

|---|---|

(a) | 在玻璃或矽晶圓上塗佈釋放層(release layer) |

(b) | 製作 UBM(Under Bump Metallization)與第一次 passivation 開口 |

(c)-(e) | 進行多層 RDL(Redistribution Layer)與 passivation 開口,通常至第 3 或第 4 層 |

(f) | 鍍銅與平坦化處理(電鍍 + CMP) |

(g) | 關鍵步驟:Hybrid bonding(包含 Cu-to-Cu bonding + Oxide bonding)→ 圖中灰白/黃色分層顯示對位與導通結構 |

(h) | 最後使用雷射除膠與晶圓分離(Laser de-bond and cleaning) |

🔍 重點資訊:

- 黃色區域:銅層(Cu)

- 灰白結構:矽層與氧化層

- 結構密度高、pitch 極小,約為 1μm 級 Cu-Cu bonding

- 實現「面對面直接堆疊(face-to-face)」的 3D IC 封裝架構

4. 技術可行性與限制分析

- 1µm hybrid bonding:目前已達實驗片水平,但大規模商用尚受限於對位誤差與界面氣泡控制。

- 液冷封裝:需解決微通道可靠性、灌注與封膠技術、長期穩定性問題。

- chiplet-as-coolant:概念具突破性,但在製程整合與熱脹冷縮管理上難度高。

- CPO 光電共封裝:現已進入原型製作,光學對準、封裝光損與熱穩定性為關鍵挑戰。

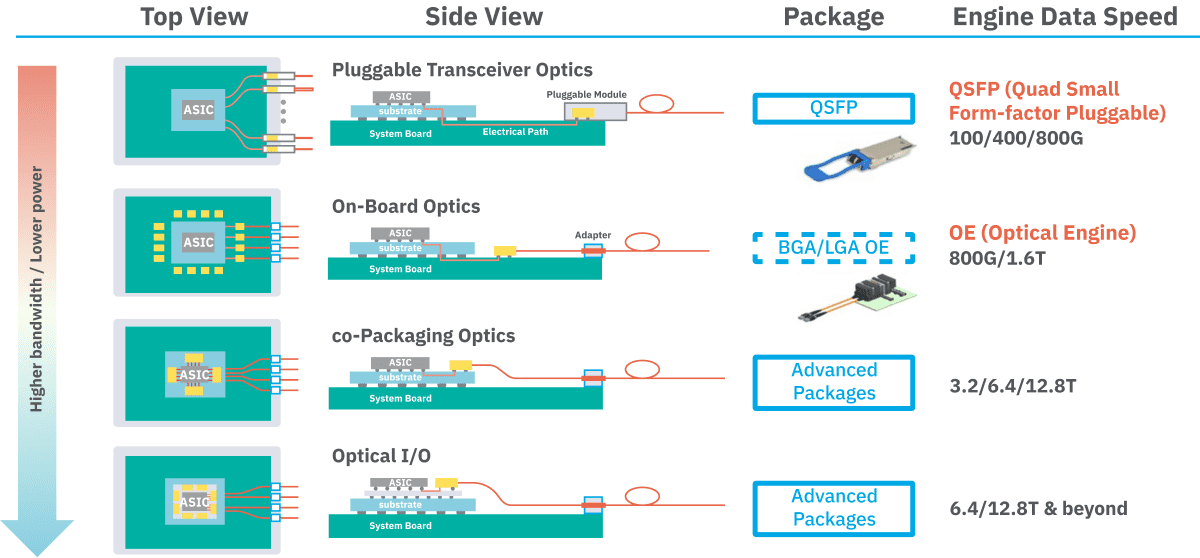

[[ Fig 4: Co-Packaged Optics 架構演進示意圖,展示從 Pluggable、On-Board 至 CPO 與 Optical I/O 各階段整合模式,並對應資料速率與封裝技術需求(出自 ASE Silicon Photonics 技術簡報) ]]

📌 圖片說明解析

這張圖來自 ASE 的官方簡報,對比了四種光模組整合架構的演進,從傳統到先進

架構 | 上視圖與側剖圖 | 封裝型式 | 資料速率 |

|---|---|---|---|

Pluggable Optics | 光模組插拔於主機板上,ASIC 與光模組相隔較遠 | QSFP | 100/400/800G |

On-Board Optics | 光引擎接近 ASIC,但仍獨立封裝 | BGA/LGA OE | 800G / 1.6T |

Co-Packaged Optics (CPO) | 光引擎直接與 ASIC 共封裝(圖中第三項) | Advanced Packages | 3.2 / 6.4 / 12.8T |

Optical I/O | 光模組進一步整合至晶片級別(具未來性) | Advanced Packages | 6.4 / 12.8T & beyond |

- 左側箭頭說明清楚傳輸趨勢: 更高頻寬、更低功耗往下演進

- 第三排正是 CPO 架構核心,與主題完全契合

5. 市場與產業影響

- 資料中心/AI 加速器市場:將是最早導入此類高密度、高散熱封裝技術的應用場域。

- 晶圓代工/封裝業者(TSMC、Intel、ASE 等):需要投入高額資本升級先進封裝產線。

材料供應商(如 Tosoh、Brewer、Shin-Etsu):須提供新一代封裝膠、熱界面材料、導熱聚合物等新材料。

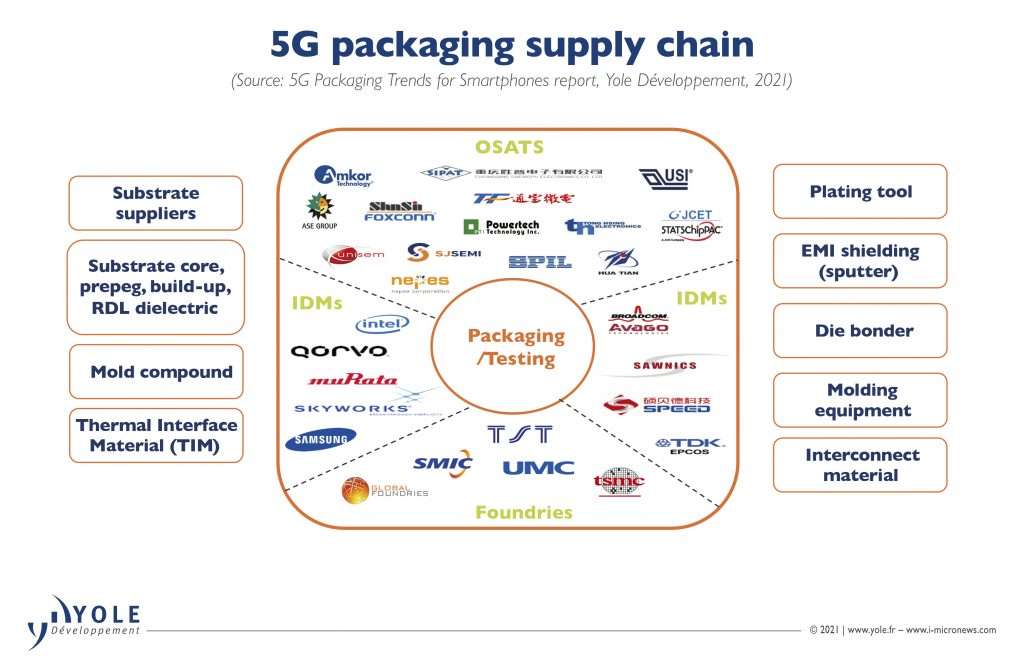

[[ Fig 5: 3D 封裝材料供應鏈圖譜,顯示材料技術、設備與製程供應商在高密度封裝產業中的角色(出自 Yole Development) ]]

6. 觀點與建議

- 本文雖屬技術新聞性質,但引用大量 ECTC 大會報告,具備極高趨勢參考價值。

- 從商業角度,液冷與 chiplet 級散熱將帶動晶圓封裝材料與系統整合解決方案的升級機會。

- 台灣廠商若要參與,建議關注如下三類技術鏈結:

- 無氟冷卻液與密封封裝材料(取代 3M Novec)

- 微通道結構用高精度雷射加工/微蝕刻技術

- 光電/熱共封裝模組整合(特別是 Co-Packaged Optics 模組)

- 機會

(1) 無氟冷卻液材料

TSMC、Imec 等先進封裝大廠已開始導入晶片內建微通道液冷結構,以因應 AI 晶片的極高功率密度需求。由於 3M 已退出 Novec 冷卻液市場,產業對無氟、絕緣型液體材料的替代方案有強烈需求,為 UNK 的熱管理材料產品帶來潛在機會。

(2)導電聚合物用於 CPO(Co-Packaged Optics)製程

ASE、Intel 等正在推動 CPO 封裝架構,將光模組與邏輯晶片共封裝以提升高速低功耗傳輸能力。製程中需導入具備高導電性、光穩定性及製程相容性的特殊導電聚合物。可思考作進一步切入光電封裝供應鏈。

Appendix

原文出處

ECTC 2025“ECTC 2025(第 75 屆 IEEE Electronic Components and Technology Conference)將於 2025年5月27日至30日在美國德州 Grapevine 的 Gaylord Texan Resort & Convention Center 舉行,由 IEEE Electronics Packaging Society 主辦。